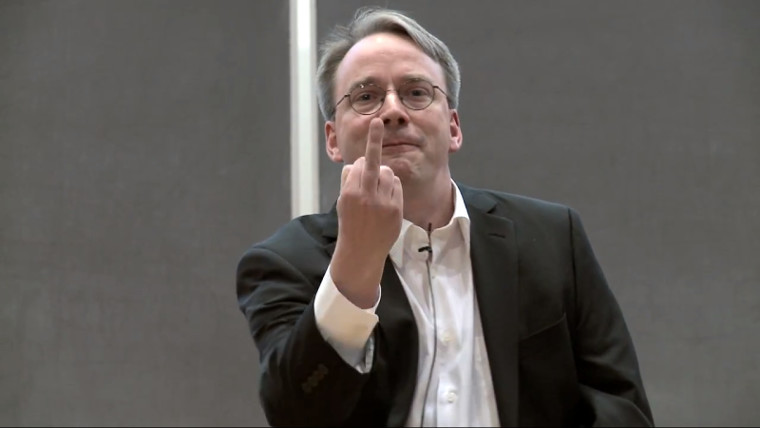

Линус Торвальдс, отец основатель Linux, один из самых экспрессивных технических руководителей, и его взгляды очень интересны, согласны вы с ними или нет.

Обсуждая изменения и дополнения к новой сборке Linux KConfig (конфигурация ядра), Торвальдс выразил свое раздражение и неодобрение уровнями функций архитектуры AMD64 или x86_64. Он написал:

Подумав еще раз, давайте не будем переходить на микроархитектурные уровни x86-64. Это глупое дело.

Все эти наименования «v2», «v3», «v4» и т. д. кажутся каким-то безумным артефактом glibc, они глупы и должны быть удалены.

Это не имеет никакого отношения ни к чему. Пожалуйста, не вносите этот «пердеж» в исходники ядра.

Я понятия не имею, кто придумал эту ерунду с «уровнями микроархитектуры», но, насколько я могу судить, это совершенно неофициальная и совершенно неработающая модель.

Существует вполне реальная модель для микроархитектурных особенностей, и это биты CPUID. Попытка линеаризировать эти биты технически неверна, поскольку эти вещи просто не являются какой-то линейной прогрессией.

И что еще хуже, это «упрощение», которое буквально добавляет сложности. Теперь вместо вопроса «поддерживает ли этот процессор инструкцию cmpxchgb16?», вопрос становится «что, черт возьми, означает „v3“ еще раз?»

Так что нет. Мы НЕ внедряем этот идиотизм в ядро.

Для тех, кому интересно, эти уровни микроархитектуры x86-64 были введены еще в 2020 году Флорианом Ваймером из Red Hat. Первоначально были предложены «Уровни A, B и C», а позже был добавлен и «Уровень D».

По сути, эти уровни классифицируют функции ЦП во временном/хронологическом порядке, чтобы упростить улучшение совместимости оборудования и ОС/программного обеспечения, а также синергии для лучшей оптимизации компиляции:

- x86-64-v2 обеспечивает поддержку (помимо прочего) векторных инструкций вплоть до Streaming SIMD Extensions 4.2 (SSE4.2) и Supplemental Streaming SIMD Extensions 3 (SSSE3), инструкции POPCNT (полезной для анализа данных и побитовой обработки в некоторых структурах данных) и CMPXCHG16B (двухсловной инструкции сравнения и обмена, полезной для параллельных алгоритмов).

- x86-64-v3 добавляет векторные инструкции до AVX2, MOVBE (для доступа к данным с обратным порядком байтов) и дополнительные инструкции по битовой манипуляции.

- x86-64-v4 включает векторные инструкции из некоторых вариантов AVX-512.

Линус Торвальдс считает, что эти уровни архитектуры скорее усложняют ситуацию, чем упрощают ее, поскольку линейная последовательность аппаратных инструкций и функций не является реалистичным подходом.

Здесь Торвальдс учитывает то, что мы часто обнаруживаем, определенные инструкции ЦП, например, AVX, могут присутствовать в некоторых семействах процессоров, но позже исчезают. Недавним примером является Intel, которая представила AVX-512 в 11-м поколении Rocket Lake, а затем удалила его в последующих поколениях.

Следует отметить, что Линус Торвальдс с недавних пор является светилом недавно созданной Консультативной группы по экосистеме x86, поэтому его вклад, безусловно, может иметь определенный вес.